White Paper: Optimal VLSI Architectural Synthesis

Author: Gebotys

Abstract

This white paper explores the critical role of architectural synthesis in Very Large-Scale Integration (VLSI) design. It delves into the challenges and opportunities associated with optimizing VLSI architectures for performance, power consumption, and area, drawing insights from Gebotys' expertise in the field. The paper presents advanced techniques and methodologies for achieving optimal architectural synthesis, enabling the design of high-performance, energy-efficient VLSI circuits.

Introduction

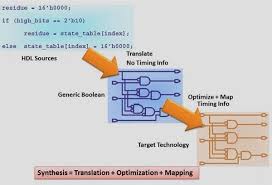

VLSI design involves creating complex integrated circuits with billions of transistors. The choice of architecture significantly impacts the performance, power consumption, and area of these circuits. Architectural synthesis is the process of transforming a high-level behavioral description of a design into a structural representation, selecting appropriate hardware components and optimizing their interconnection. This paper aims to provide a comprehensive overview of optimal VLSI architectural synthesis, covering key techniques, challenges, and best practices.

Key Challenges in VLSI Architectural Synthesis

- Design Complexity: Modern VLSI designs are increasingly complex, with millions or billions of transistors. This complexity makes it difficult to manually optimize architectures.

- Performance-Power-Area (PPA) Trade-offs: Designers often face conflicting requirements for performance, power consumption, and area. Achieving optimal trade-offs requires careful consideration and optimization.

- Design Space Exploration: The vast design space of possible architectures makes it challenging to explore all options and identify the best solution.

- Timing Constraints: Ensuring that the circuit meets timing requirements is critical for correct operation. Architectural synthesis must consider timing constraints and optimize the design accordingly.

Optimal VLSI Architectural Synthesis Techniques

- High-Level Synthesis (HLS): HLS transforms behavioral descriptions written in high-level languages (e.g., C, C++) into hardware implementations. It offers greater flexibility and productivity compared to traditional RTL design.

- Architectural Exploration: Tools and techniques for exploring different architectural options and evaluating their performance, power, and area.

- Floorplanning and Placement: Optimizing the physical layout of components on the chip to minimize interconnect length and improve performance.

- Clock Gating: Techniques for reducing power consumption by selectively disabling unused circuit elements.

- Power Optimization: Exploring various power optimization techniques, such as voltage scaling, dynamic voltage and frequency scaling (DVFS), and power gating.

Best Practices for Optimal VLSI Architectural Synthesis

- Early Design Space Exploration: Start exploring architectural options early in the design process to identify potential bottlenecks and optimize the design.

- Consideration of PPA Trade-offs: Carefully evaluate the trade-offs between performance, power, and area to achieve the desired balance.

- Use of Advanced Synthesis Tools: Leverage modern synthesis tools with advanced optimization capabilities.

- Verification and Validation: Thoroughly verify the synthesized design to ensure it meets functional and performance requirements.

- Iterative Refinement: Continuously refine the design based on simulation results and feedback to achieve optimal performance.

Conclusion

Optimal VLSI architectural synthesis is crucial for designing high-performance, energy-efficient, and area-efficient integrated circuits. By addressing the challenges and leveraging advanced techniques, designers can create innovative and competitive VLSI products. This white paper has provided an overview of key concepts, techniques, and best practices for achieving optimal VLSI architectural synthesis. Please contact ias-research.com for details.

References

- Gebotys, B. (Book title)

- VLSI Design: [invalid URL removed]

- IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems: [invalid URL removed]

- Cadence Design Systems: https://www.synopsys.com/